# 60V - 60W DMOS AUDIO AMPLIFIER WITH MUTE/ST-BY

- VERY HIGH OPERATING VOLTAGE RANGE (±30V)

- DMOS POWER STAGE

- HIGH OUTPUT POWER (THD = 10%, UP TO 60W)

- MUTING/STAND-BY FUNCTIONS

- NO SWITCH ON/OFF NOISE

- VERY LOW DISTORTION

- VERY LOW NOISE

- SHORT CIRCUIT PROTECTION

- THERMAL SHUTDOWN

- CLIP DETECTOR

- MODULARITY (MORE DEVICES CAN BE EASILY CONNECTED IN PARALLEL TO DRIVE VERY LOW IMPEDANCES)

#### **DESCRIPTION**

The TDA7296S is a monolithic integrated circuit in Multiwatt15 package, intended for use as audio class AB amplifier in Hi-Fi field applications (Home Stereo, self powered loudspeakers, Top-

#### MULTIPOWER BCD TECHNOLOGY

class TV). Thanks to the wide voltage range and to the high out current capability it is able to supply the highest power into both  $4\Omega$  and  $8\Omega$  loads.

The built in muting function with turn on delay simplifies the remote operation avoiding switching on-off noises.

Parallel mode is made possible by connecting more device through of pin11. High output power can be delivered to very low impedance loads, so optimizing the thermal dissipation of the system.

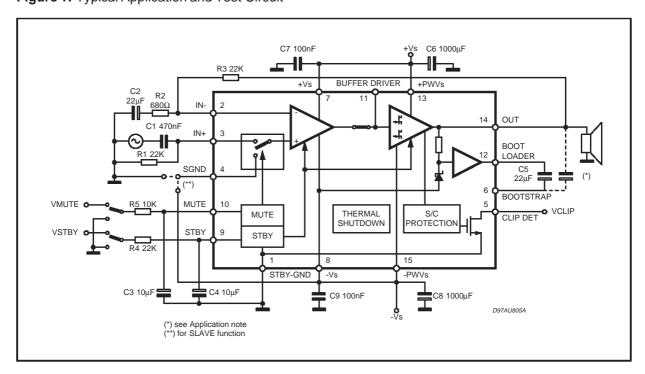

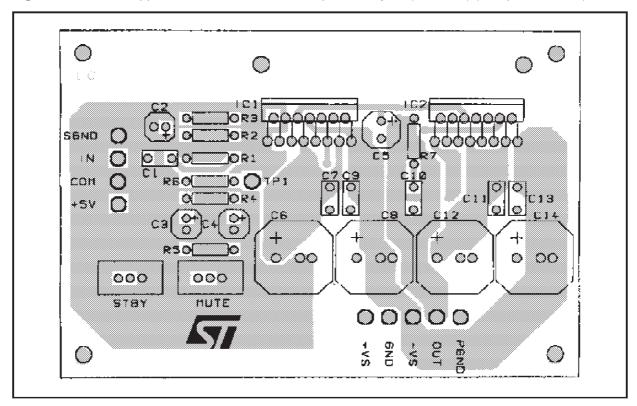

Figure 1: Typical Application and Test Circuit

June 2000 1/11

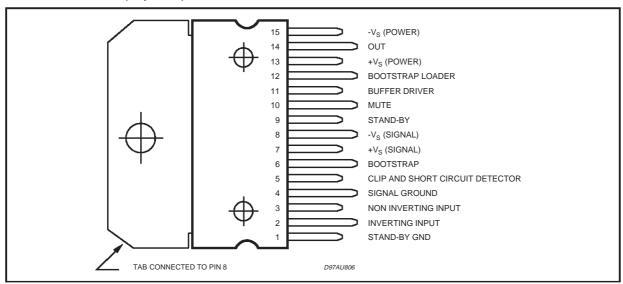

# PIN CONNECTION (Top view)

# **QUICK REFERENCE DATA**

| Symbol            | Parameter                | Test Conditions                                  | Min. | Тур. | Max. | Unit |

|-------------------|--------------------------|--------------------------------------------------|------|------|------|------|

| Vs                | Supply Voltage Operating |                                                  | ±12  |      | ± 30 | V    |

| G <sub>LOOP</sub> | Closed Loop Gain         |                                                  | 26   |      | 40   | dB   |

| P <sub>tot</sub>  | Output Power             | $V_S = \pm 30V$ ; $R_L = 8\Omega$ ; $THD = 10\%$ |      | 60   |      | W    |

|                   |                          | $V_S = \pm 25V$ ; $R_L = 4\Omega$ ; $THD = 10\%$ |      | 60   |      | W    |

| SVR               | Supply Voltage Rejection |                                                  |      | 75   |      | dB   |

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                     | Value   | Unit |

|------------------|-----------------------------------------------|---------|------|

| Vs               | Supply Voltage (No Signal)                    | ±35     | V    |

| V <sub>1</sub>   | VSTAND-BY GND Voltage Referred to -Vs (pin 8) | 60      | V    |

| V <sub>2</sub>   | Input Voltage (inverting) Referred to -Vs     | 60      | V    |

| V2 - V3          | Maximum Differential Inputs                   | ±30     | V    |

| V3               | Input Voltage (non inverting) Referred to -Vs | 60      | V    |

| V <sub>4</sub>   | Signal GND Voltage Referred to -Vs            | 60      | V    |

| V <sub>5</sub>   | Clip Detector Voltage Referred to -Vs         | 60      | V    |

| V <sub>6</sub>   | Bootstrap Voltage Referred to -Vs             | 60      | V    |

| V9               | Stand-by Voltage Referred to -Vs              | 60      | V    |

| V <sub>10</sub>  | Mute Voltage Referred to -Vs                  | 60      | V    |

| V11              | Buffer Voltage Referred to -Vs                | 60      | V    |

| V12              | Bootstrap Loader Voltage Referred to -Vs      | 60      | V    |

| Io               | Output Peak Current                           | 10      | А    |

| P <sub>tot</sub> | Power Dissipation T <sub>case</sub> = 70°C    | 50      | W    |

| T <sub>op</sub>  | Operating Ambient Temperature Range           | 0 to 70 | °C   |

| $T_{stg}, T_{j}$ | Storage and Junction Temperature              | 150     | °C   |

# **THERMAL DATA**

| Symbol                 | Description                      |   | Max | Unit |

|------------------------|----------------------------------|---|-----|------|

| R <sub>th i-case</sub> | Thermal Resistance Junction-case | 1 | 1.5 | °C/W |

2/11

# **ELECTRICAL CHARACTERISTICS** (Refer to the Test Circuit $V_S = \pm 24V$ , $R_L = 8\Omega$ , $G_V = 30 dB$ ; $R_g = 50 \Omega$ ; $T_{amb} = 25^{\circ}C$ , f = 1 kHz; unless otherwise specified).

| Symbol                          | Parameter                                                                                         | Test Condition                                                                                                                                                 | Min.           | Тур.           | Max. | Unit        |

|---------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|------|-------------|

| Vs                              | Operating Supply Range                                                                            |                                                                                                                                                                | ±10            |                | ±30  | V           |

| Iq                              | Quiescent Current                                                                                 |                                                                                                                                                                | 20             | 30             | 60   | mA          |

| I <sub>b</sub>                  | Input Bias Current                                                                                |                                                                                                                                                                |                |                | 500  | nA          |

| Vos                             | Input Offset Voltage                                                                              |                                                                                                                                                                |                |                | ±10  | mV          |

| Ios                             | Input Offset Current                                                                              |                                                                                                                                                                |                |                | ±100 | nA          |

| Po                              | RMS Continuous Output Power                                                                       | $\begin{array}{l} d = 0.5\%; \\ V_S = \pm  24V,  R_L = 8\Omega \\ V_S = \pm  21V,  R_L = 6\Omega \\ V_S = \pm  18V,  R_L = 4\Omega \end{array}$                | 27<br>27<br>27 | 30<br>30<br>30 |      | W<br>W<br>W |

|                                 | Music Power (RMS) (*)<br>Δt = 1s                                                                  | $ \begin{array}{l} d = 10\%; \\ R_L = 8\Omega \; ; \; V_S = \pm 30V \\ R_L = 6\Omega \; ; \; V_S = \pm 24V \\ R_L = 4\Omega; \; \; V_S = \pm 23V \end{array} $ |                | 60<br>60<br>60 |      | W<br>W<br>W |

| d                               | Total Harmonic Distortion (**) $P_0 = 5W$ ; $f = 1kHz$<br>$P_0 = 0.1$ to 20W; $f = 20Hz$ to 20kHz |                                                                                                                                                                |                | 0.005          | 0.1  | %<br>%      |

|                                 |                                                                                                   | $V_S = \pm 18V, R_L = 4\Omega$ :<br>$P_O = 5W; f = 1kHz$<br>$P_O = 0.1$ to 20W; $f = 20Hz$ to 20kHz                                                            |                | 0.01           | 0.1  | %<br>%      |

| SR                              | Slew Rate                                                                                         |                                                                                                                                                                | 7              | 10             |      | V/μs        |

| Gv                              | Open Loop Voltage Gain                                                                            |                                                                                                                                                                |                | 80             |      | dB          |

| G∨                              | Closed Loop Voltage Gain                                                                          |                                                                                                                                                                | 24             | 30             | 40   | dB          |

| e <sub>N</sub>                  | Total Input Noise                                                                                 | A = curve<br>f = 20Hz to 20kHz                                                                                                                                 |                | 1<br>2         | 5    | μV<br>μV    |

| f <sub>L</sub> , f <sub>H</sub> | Frequency Response (-3dB)                                                                         | P <sub>O</sub> = 1W                                                                                                                                            |                | 20Hz to 20kHz  |      |             |

| Ri                              | Input Resistance                                                                                  |                                                                                                                                                                | 100            |                |      | kΩ          |

| SVR                             | Supply Voltage Rejection                                                                          | $f = 100Hz; V_{ripple} = 0.5Vrms$                                                                                                                              | 60             | 75             |      | dB          |

| T <sub>S</sub>                  | Thermal Shutdown                                                                                  |                                                                                                                                                                |                | 150            |      | °C          |

| STAND-B                         | Y FUNCTION (Ref: -V <sub>S</sub> or GND)                                                          |                                                                                                                                                                |                |                |      |             |

| V <sub>ST on</sub>              | Stand-by on Threshold                                                                             |                                                                                                                                                                |                |                | 1.5  | V           |

| V <sub>ST off</sub>             | Stand-by off Threshold                                                                            |                                                                                                                                                                | 3.5            |                |      | V           |

| ATT <sub>st-by</sub>            | Stand-by Attenuation                                                                              |                                                                                                                                                                | 70             | 90             |      | dB          |

| I <sub>q st-by</sub>            | Quiescent Current @ Stand-by                                                                      |                                                                                                                                                                |                | 1              | 3    | mA          |

| MUTE FL                         | INCTION (Ref: -V <sub>S</sub> or GND)                                                             |                                                                                                                                                                |                |                |      |             |

| $V_{Mon}$                       | Mute on Threshold                                                                                 |                                                                                                                                                                |                |                | 1.5  | V           |

| $V_{Moff}$                      | Mute off Threshold                                                                                |                                                                                                                                                                | 3.5            |                |      | V           |

| ATT <sub>mute</sub>             | Mute Attenuation                                                                                  |                                                                                                                                                                | 60             | 80             |      | dB          |

Note (\*\*):

MUSIC POWER is the maximal power which the amplifier is capable of producing across the rated load resistance (regardless of non linearity)

1 sec after the application of a sinusoidal input signal of frequency 1KHz.

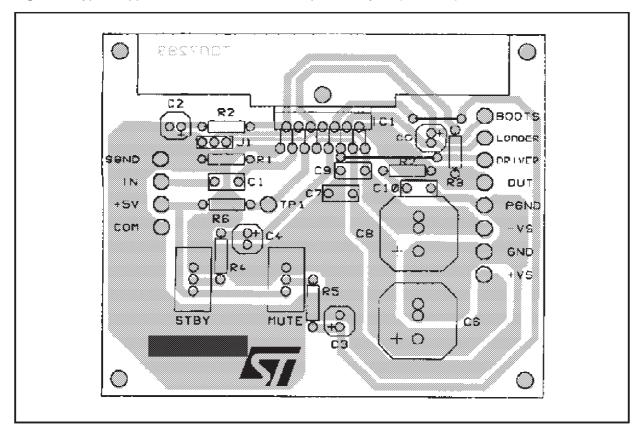

Note (\*\*): Tested with optimized Application Board (see fig. 2)

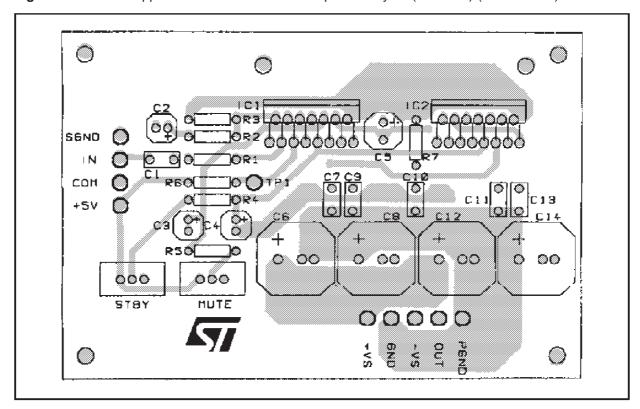

Figure 2: Typical Application P.C. Board and Component Layout (scale 1:1)

# APPLICATION SUGGESTIONS (see Test and Application Circuits of the Fig. 1)

The recommended values of the external components are those shown on the application circuit of Figure 1. Different values can be used; the following table can help the designer.

| COMPONENTS | SUGGESTED VALUE | PURPOSE                   | LARGER THAN<br>SUGGESTED    | SMALLER THAN<br>SUGGESTED                  |

|------------|-----------------|---------------------------|-----------------------------|--------------------------------------------|

| R1 (*)     | 22k             | INPUT RESISTANCE          | INCREASE INPUT<br>IMPEDANCE | DECREASE INPUT<br>IMPEDANCE                |

| R2         | 680Ω            | CLOSED LOOP GAIN          | DECREASE OF GAIN            | INCREASE OF GAIN                           |

| R3 (*)     | 22k             | SET TO 30dB (**)          | INCREASE OF GAIN            | DECREASE OF GAIN                           |

| R4         | 22k             | ST-BY TIME<br>CONSTANT    | LARGER ST-BY<br>ON/OFF TIME | SMALLER ST-BY<br>ON/OFF TIME;<br>POP NOISE |

| R5         | 10k             | MUTE TIME<br>CONSTANT     | LARGER MUTE<br>ON/OFF TIME  | SMALLER MUTE<br>ON/OFF TIME                |

| C1         | 0.47μF          | INPUT DC<br>DECOUPLING    |                             | HIGHER LOW<br>FREQUENCY<br>CUTOFF          |

| C2         | 22μF            | FEEDBACK DC<br>DECOUPLING |                             | HIGHER LOW<br>FREQUENCY<br>CUTOFF          |

| C3         | 10μF            | MUTE TIME<br>CONSTANT     | LARGER MUTE<br>ON/OFF TIME  | SMALLER MUTE<br>ON/OFF TIME                |

| C4         | 10μF            | ST-BY TIME<br>CONSTANT    | LARGER ST-BY<br>ON/OFF TIME | SMALLER ST-BY<br>ON/OFF TIME;<br>POP NOISE |

| C5         | 22μFXN (***)    | BOOTSTRAPPING             |                             | SIGNAL<br>DEGRADATION AT<br>LOW FREQUENCY  |

| C6, C8     | 1000μF          | SUPPLY VOLTAGE<br>BYPASS  |                             |                                            |

| C7, C9     | 0.1μF           | SUPPLY VOLTAGE<br>BYPASS  |                             | DANGER OF<br>OSCILLATION                   |

<sup>(\*)</sup> R1 = R3 for pop optimization

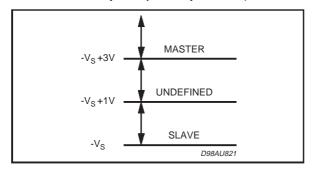

# Slave function: pin 4 (Ref to pin 8 -Vs)

### Note:

If in the application, the speakers are connected via long wires, it is a good rule to add between the output and GND, a Boucherot Cell, in order to avoid dangerous spurious oscillations when the speakers terminal are shorted.

The suggested Boucherot Resistor is  $3.9\Omega/2W$  and the capacitor is  $1\mu F$ .

<sup>(\*\*)</sup> Closed Loop Gain has to be ≥ 26dB

<sup>(\*\*\*)</sup> Multiply this value for the number of modular part connected

#### INTRODUCTION

In consumer electronics, an increasing demand has arisen for very high power monolithic audio amplifiers able to match, with a low cost, the performance obtained from the best discrete designs.

The task of realizing this linear integrated circuit in conventional bipolar technology is made extremely difficult by the occurence of 2nd breakdown phoenomenon. It limits the safe operating area (SOA) of the power devices, and, as a consequence, the maximum attainable output power, especially in presence of highly reactive loads.

Moreover, full exploitation of the SOA translates into a substantial increase in circuit and layout complexity due to the need of sophisticated protection circuits.

To overcome these substantial drawbacks, the use of power MOS devices, which are immune from secondary breakdown is highly desirable.

#### 1) Output Stage

The main design task in developping a power operational amplifier, independently of the technology used, is that of realization of the output stage.

The solution shown as a principle shematic by Fig3 represents the DMOS unity - gain output buffer of the TDA7296S.

This large-signal, high-power buffer must be capable of handling extremely high current and voltage levels while maintaining acceptably low harmonic distortion and good behaviour over frequency response; moreover, an accurate control of quiescent current is required.

A local linearizing feedback, provided by differential amplifier A, is used to fullfil the above requirements, allowing a simple and effective quiescent current setting.

Proper biasing of the power output transistors alone is however not enough to guarantee the absence of crossover distortion.

While a linearization of the DC transfer characteristic of the stage is obtained, the dynamic behaviour of the system must be taken into account.

A significant aid in keeping the distortion contributed by the final stage as low as possible is provided by the compensation scheme, which exploits the direct connection of the Miller capacitor at the amplifier's output to introduce a local AC feedbackpath enclosing the output stage itself.

#### 2) Protections

In designing a power IC, particular attention must be reserved to the circuits devoted to protection of the device from short circuit or overload conditions.

Due to the absence of the 2nd breakdown phenomenon, the SOA of the power DMOS transistors is delimited only by a maximum dissipation curve dependent on the duration of the applied stimulus.

In order to fully exploit the capabilities of the power transistors, the protection scheme implemented in this device combines a conventional SOA protection circuit with a novel local temperature sensing technique which "dynamically" controls the maximum dissipation.

In addition to the overload protection described

Figure 3: Principle Schematic of a DMOS unity-gain buffer.

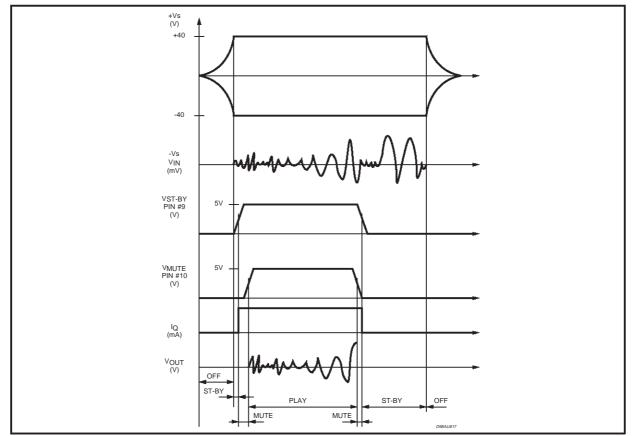

Figure 4: Turn ON/OFF Suggested Sequence

above, the device features a thermal shutdown circuit which initially puts the device into a muting state (@ Tj = 150 °C) and then into stand-by (@ Tj = 160 °C).

Full protection against electrostatic discharges on every pin is included.

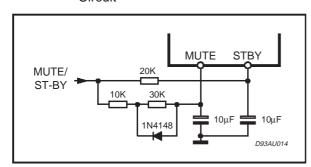

Figure 5: Single Signal ST-BY/MUTE Control Circuit

#### 3) Other Features

The device is provided with both stand-by and mute functions, independently driven by two CMOS logic compatible input pins.

The circuits dedicated to the switching on and off of the amplifier have been carefully optimized to

avoid any kind of uncontrolled audible transient at the output.

The sequence that we recommend during the ON/OFF transients is shown by Figure 4.

The application of figure 5 shows the possibility of using only one command for both st-by and mute functions. On both the pins, the maximum applicable range corresponds to the operating supply voltage.

#### **APPLICATION INFORMATION**

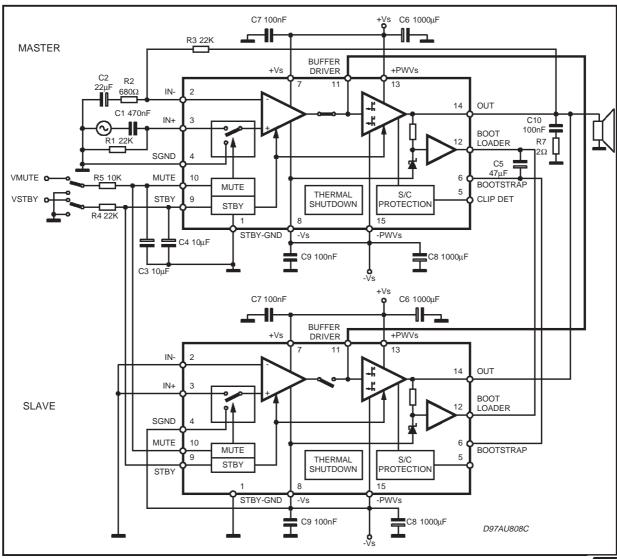

#### **BRIDGE APPLICATION**

Another application suggestion is the BRIDGE configuration, where two TDA7296S are used. In this application, the value of the load must not be lower than 8 Ohm for dissipation and current capability reasons.

A suitable field of application includes HI-FI/TV subwoofers realizations.

The main advantages offered by this solution are:

- High power performances with limited supply voltage level.

- Considerably high output power even with high load values (i.e. 16 Ohm).

With RI= 8 Ohm,  $Vs = \pm 23V$  the maximum output power obtainable is 120W (Music Power)

#### APPLICATION NOTE: (ref. fig. 7)

### **Modular Application (more Devices in Parallel)**

The use of the modular application lets very high power be delivered to very low impedance loads. The modular application implies one device to act as a master and the others as slaves.

The slave power stages are driven by the master device and work in parallel all together, while the input and the gain stages of the slave device are disabled, the figure below shows the connections required to configure two devices to work together.

- The master chip connections are the same as the normal single ones.

- The outputs can be connected together without the need of any ballast resistance.

- The slave SGND pin must be tied to the negative supply.

- The slave ST-BY pin must be connected to ST-BY pin.

- The bootstrap lines must be connected together and the bootstrap capacitor must be increased: for N devices the boostrap capacitor must be 22μF times N.

- The slave Mute and IN-pins must be grounded.

#### THE BOOTSTRAP CAPACITOR

For compatibility purpose with the previous devices of the family, the boostrap capacitor can be connected both between the bootstrap pin (6) and the output pin (14) or between the boostrap pin (6) and the bootstrap loader pin (12).

Figure 6: Modular Application Circuit

Figure 7a: Modular Application P.C. Board and Component Layout (scale 1:1) (Component SIDE)

Figure 7b: Modular Application P.C. Board and Component Layout (scale 1:1) (Solder SIDE)

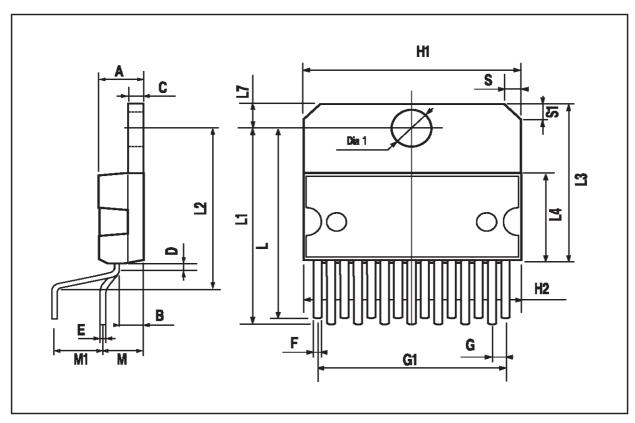

| DIM.   | mm    |       |       | inch  |       |       |

|--------|-------|-------|-------|-------|-------|-------|

| DIIVI. | MIN.  | TYP.  | MAX.  | MIN.  | TYP.  | MAX.  |

| Α      |       |       | 5     |       |       | 0.197 |

| В      |       |       | 2.65  |       |       | 0.104 |

| С      |       |       | 1.6   |       |       | 0.063 |

| D      |       | 1     |       |       | 0.039 |       |

| Е      | 0.49  |       | 0.55  | 0.019 |       | 0.022 |

| F      | 0.66  |       | 0.75  | 0.026 |       | 0.030 |

| G      | 1.02  | 1.27  | 1.52  | 0.040 | 0.050 | 0.060 |

| G1     | 17.53 | 17.78 | 18.03 | 0.690 | 0.700 | 0.710 |

| H1     | 19.6  |       |       | 0.772 |       |       |

| H2     |       |       | 20.2  |       |       | 0.795 |

| L      | 21.9  | 22.2  | 22.5  | 0.862 | 0.874 | 0.886 |

| L1     | 21.7  | 22.1  | 22.5  | 0.854 | 0.870 | 0.886 |

| L2     | 17.65 |       | 18.1  | 0.695 |       | 0.713 |

| L3     | 17.25 | 17.5  | 17.75 | 0.679 | 0.689 | 0.699 |

| L4     | 10.3  | 10.7  | 10.9  | 0.406 | 0.421 | 0.429 |

| L7     | 2.65  |       | 2.9   | 0.104 |       | 0.114 |

| М      | 4.25  | 4.55  | 4.85  | 0.167 | 0.179 | 0.191 |

| M1     | 4.63  | 5.08  | 5.53  | 0.182 | 0.200 | 0.218 |

| S      | 1.9   |       | 2.6   | 0.075 |       | 0.102 |

| S1     | 1.9   |       | 2.6   | 0.075 |       | 0.102 |

| Dia1   | 3.65  |       | 3.85  | 0.144 |       | 0.152 |

# OUTLINE AND MECHANICAL DATA

10/11

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

© 2000 STMicroelectronics — Printed in Italy — All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A. http://www.st.com

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.